и®ўйҳ…з”өеӯҗжҠҘпјҢжҺҢжҸЎжңҖ新科жҠҖдёҺдә§дёҡи¶ӢеҠҝ

Astera Labs

2019/10/29

Astera LabsжҺЁеҮәе…Ёзҗғ第дёҖдёӘйҖӮз”ЁдәҺPCI Express 4.0е’Ң5.0и§ЈеҶіж–№жЎҲзҡ„жҷәиғҪеӨҚдҪҚж—¶еҷЁдә§е“Ғз»„еҗҲ

дё“дёәе·ҘдҪңиҙҹиҪҪдјҳеҢ–е№іеҸ°иҖҢи®ҫи®ЎпјҢд»Ҙж”ҜжҢҒй«ҳеёҰе®ҪгҖҒи¶…дҪҺ延иҝҹзҡ„ж–°жңҚеҠЎеҷЁйӘЁе№І

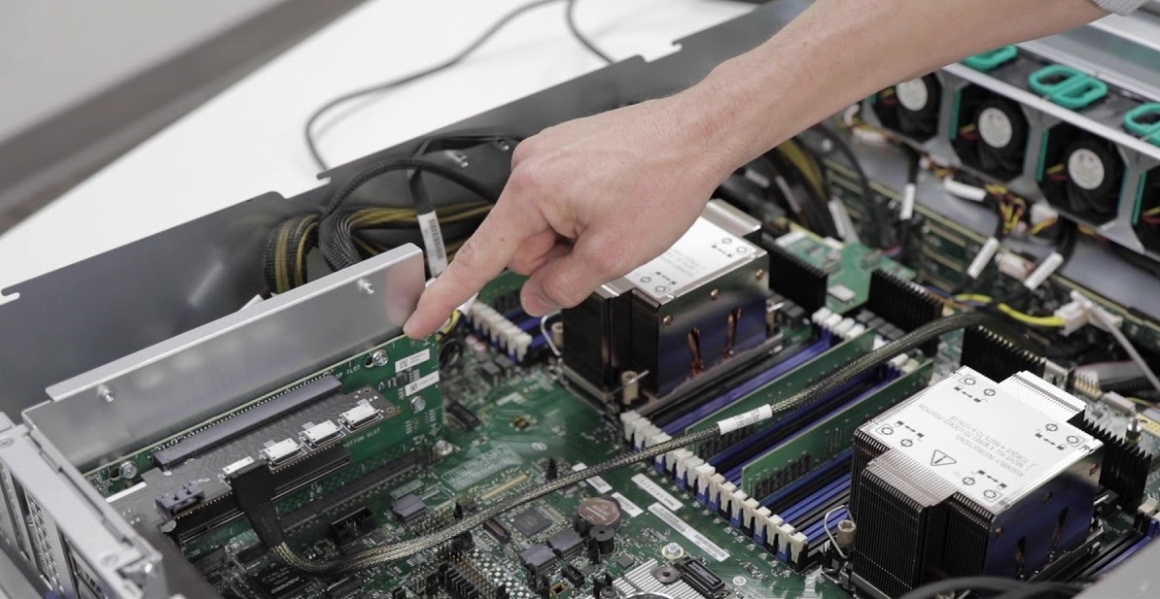

Astera LabsжҷәиғҪзҪ‘з»ңж•°жҚ®еҲҶеҸ‘зҡ„йўҶеҜјеҺӮе•ҶпјҢд»Ҡж—ҘжҺЁеҮәй’ҲеҜ№PCI Express® (PCIe®) 4.0е’Ң5.0жҠҖжңҜзҡ„Ariesжҷәж…§еӨҚдҪҚж—¶еҷЁ(Smart Retimer)дә§е“Ғз»„еҗҲгҖӮAriesжҷәиғҪеӨҚдҪҚж—¶еҷЁдё»иҰҒеңЁдҪҝзі»з»ҹи®ҫи®Ўдәәе‘ҳеҚідҪҝеңЁPCIe 5.0жҠҖжңҜзҡ„32 GT/sйҖҹеәҰдёӢпјҢд№ҹеҸҜд»ҘиҪ»жқҫең°е°Ҷи®ҜеҸ·дј иҫ“и·қзҰ»еҠ еҖҚ并е®һзҺ°еҚіжҸ’еҚіз”Ёдә’ж“ҚдҪңпјҢиҖҢдёҚдјҡеҪұе“Қдә’иҝһжӢ“жү‘гҖӮAstera LabsжҳҜ第дёҖ家дёәжңҖй«ҳ32дёӘеҸҢеҗ‘йҖҡйҒ“зҡ„PCIe 4.0е’Ң5.0еә”з”ЁжҸҗдҫӣе®һз”Ёзҡ„жҷәиғҪеӨҚдҪҚж—¶еҷЁSoCзҡ„е…¬еҸёгҖӮ

Astera Labsжү§иЎҢй•ҝJitendra MohanиЎЁзӨәпјҡгҖҢAstera LabsиҮҙеҠӣдәҺж¶ҲйҷӨ瓶йўҲпјҢж— и®әе®ғ们еҮәзҺ°еңЁзі»з»ҹдёӯзҡ„е“ӘдёӘдҪҚзҪ®гҖӮжҲ‘们没жңүйҖҸиҝҮеўһйҮҸж–№жі•жқҘеўһеҠ еёҰе®ҪиғҪеҠӣпјҢиҖҢжҳҜйҮҮз”ЁдёҖз§Қе…Ёж–°зҡ„ж–№жі•жқҘдјҳеҢ–жҲ‘们зҡ„еӨҚдҪҚж—¶еҷЁпјҢд»ҘйҖӮз”ЁдәҺйңҖиҰҒдҪҺ延иҝҹе’Ңдә‘з«Ҝ规模管зҗҶиғҪеҠӣзҡ„е·ҘдҪңиҙҹиҪҪдјҳеҢ–е№іеҸ°гҖӮжҲ‘们зҡ„Ariesдә§е“Ғз»„еҗҲеңЁдә‘з«Ҝдёӯи®ҫ计并且жңҚеҠЎдәҺдә‘з«ҜпјҢе®ғи®©жҲ‘们жҲҗдёәPCIeеӨҚдҪҚж—¶еҷЁдә§дёҡи§ЈеҶіж–№жЎҲзҡ„е…Ҳй©ұгҖӮгҖҚ

ж–°й—»дә®зӮ№

ејӮиҙЁиҝҗз®—е’Ңе·ҘдҪңиҙҹиҪҪдјҳеҢ–е№іеҸ°жӯЈеңЁйҮҚж–°е®ҡд№үдёӢдёҖд»ЈжңҚеҠЎеҷЁдёӯзҡ„иҝһжҺҘйӘЁе№ІгҖӮиҝҷз§Қж–°зҡ„йӘЁе№ІйңҖиҰҒжӣҙеҝ«йҖҹеәҰе’ҢжӣҙдҪҺ延иҝҹзҡ„дә’иҝһгҖӮйҖҹеәҰдёә16 GT/sзҡ„PCIe 4.0е’Ң32 GT/sзҡ„PCIe 5.0зҡ„йғЁзҪІжңүеҠ©дәҺе®һзҺ°иҝҷз§Қй«ҳйҖҹиҝһжҺҘпјҢдҪҶйңҖиҰҒй«ҳйҖҹи®ҜеҸ·дј иҫ“и·қзҰ»жү©еұ•и§ЈеҶіж–№жЎҲжқҘе…ӢжңҚи®ҜеҸ·е®Ңж•ҙжҖ§зҡ„жҢ‘жҲҳгҖӮеӨҚдҪҚж—¶еҷЁеңЁPCIe 4.0规иҢғдёӯиў«йҰ–ж¬Ўе®ҡд№үпјҢе®ғйҖҸиҝҮиЎҘеҒҝи®ҜеҸ·жҚҹеӨұпјҢйҮҚж–°дј иҫ“и®ҜеҸ·зҡ„ж–°еүҜжң¬пјҢд»ҺиҖҢжңүж•Ҳең°е°Ҷroot-complexе’Ңend-pointи®ҫеӨҮд№Ӣй—ҙзҡ„и·қзҰ»еҠ еҖҚгҖӮ- AriesжҷәиғҪеӨҚдҪҚж—¶еҷЁи®ҫи®Ўз”ЁдәҺиҪ»жқҫж¶ҲйҷӨд»Ҙж•°жҚ®дёәдёӯеҝғзҡ„еә”з”ЁдёӯPCIe 4.0е’ҢPCIe 5.0дә’иҝһзҡ„и®ҜеҸ·е®Ңж•ҙжҖ§й—®йўҳгҖӮ

- йҮҮз”ЁеҲӣж–°зҡ„жһ¶жһ„пјҢдҪҝеӨҚдҪҚж—¶еҷЁе№іеҸ°иғҪеӨҹеӯҰд№ гҖҒиҮӘеҠЁйҖӮеә”е’ҢйҖүжӢ©дјҳеҢ–еҗҺзҡ„и°ғж•ҙпјҢд»Ҙе®һзҺ°зЁіеҒҘзҡ„иҝһз»“е’ҢеҚіжҸ’еҚіз”Ёзҡ„дә’ж“ҚдҪң

- дёҺе…¶д»–и§ЈеҶіж–№жЎҲзӣёжҜ”пјҢеҠҹиҖ—йҷҚдҪҺдәҶдёҖеҚҠпјҢ延иҝҹеӨ§е№…йҷҚдҪҺпјҢ并且дҪҝз”Ёзҡ„组件еҮҸе°‘дәҶдёҖеҚҠгҖӮ

- и®©ж•°жҚ®дёӯеҝғзі»з»ҹи®ҫи®Ўдәәе‘ҳеҸҜд»ҘиҝӣиЎҢеүҚзһ»жҖ§зҡ„зі»з»ҹи®ҫи®ЎпјҢжүҖжҸҗдҫӣзҡ„и·қзҰ»жү©еұ•и§ЈеҶіж–№жЎҲеҸҜиҪ»жқҫгҖҒеҝ«йҖҹең°д»ҺPCIe 4.0жү©еұ•еҲ°5.0жһ¶жһ„гҖӮ

- и®ҫи®Ўдёәж”ҜжҢҒиҢғеӣҙе№ҝжіӣзҡ„зі»з»ҹжӢ“жү‘е’Ңеә”з”ЁпјҢеҢ…жӢ¬жүҖжңүPCIeйў‘зҺҮжЁЎејҸпјҲSRISгҖҒе…¬е…ұйў‘зҺҮе’ҢSRNSпјүпјҢеӨҡз§ҚеҲҶеІ”з»„еҗҲпјҲ1x16гҖҒ2x8гҖҒ4x4зӯүпјүд»ҘеҸҠIntel®еӨҚдҪҚж—¶еҷЁи§„иҢғгҖӮ

- PCIe 4.0зҡ„AriesеӨҚдҪҚж—¶еҷЁзӣ®еүҚжӯЈжҲҗеҠҹең°з”ЁеңЁе®ўжҲ·зҡ„и®ҫи®ЎдёӯгҖӮ

- Astera Labsе·ІдёҺAmazon Web Services (AWS)е’Ңе…Ёзҗғ第дёҖеӨ§еҚҠеҜјдҪ“д»Је·ҘеҺӮеҸ°з§Ҝз”ө(TSMC)еҗҲдҪңпјҢд»ҘжҺЁеҮәеңЁж•ҙдёӘдҫӣеә”й“ҫдёӯе…·жңүеҲӣж–°жҖ§зҡ„и§ЈеҶіж–№жЎҲгҖӮ

- Astera Labsд»…еңЁдә‘з«ҜдёӯиҝӣиЎҢдә§е“ҒејҖеҸ‘пјҢжҳҜйҰ–жү№е®Ңе…ЁеңЁдә‘з«ҜдёӯејҖеҸ‘еӨҚжқӮSoC并е®һзҺ°й«ҳеәҰиҗҘиҝҗзҒөжҙ»жҖ§зҡ„е…¬еҸёд№ӢдёҖгҖӮиҝҷз§Қж–№ејҸдҪҝеҫ—Astera LabsеҸҜд»ҘеҠ еҝ«дә§е“ҒдёҠеёӮж—¶й—ҙпјҢйҷҚдҪҺжҲҗжң¬пјҢ并иҝӣиЎҢж·ұе…Ҙзҡ„жЁЎжӢҹпјҢд»ҘзЎ®дҝқй«ҳиҙЁйҮҸзҡ„и®ҫи®ЎгҖӮ

- Astera LabsдёҺеҸ°з§Ҝз”өеҗҲдҪңпјҢеҲ©з”ЁеҸ°з§Ҝз”өдёҡз•ҢйўҶе…Ҳзҡ„еҲ¶зЁӢжҠҖжңҜиҝӣиЎҢжҷәж…§еӨҚдҪҚж—¶еҷЁзҡ„з”ҹдә§пјҢд»ҺиҖҢдҪҝе…¶иғҪеӨҹиҝ…йҖҹжҸҗй«ҳдә§йҮҸд»Ҙж»Ўи¶іе®ўжҲ·йңҖжұӮгҖӮ

еҸ°з§Ҝз”өеҢ—зҫҺдёҡеҠЎз®ЎзҗҶиө„ж·ұеүҜжҖ»иЈҒBradford PaulsenиЎЁзӨәпјҡгҖҢжҲ‘们дёҺAstera LabsеҗҲдҪңеҲ¶йҖ е…¶AriesжҷәиғҪеӨҚдҪҚж—¶еҷЁзҡ„з»“жһңд»ӨжҲ‘们ж„ҹеҲ°йқһеёёй«ҳе…ҙпјҢиҜҘдә§е“Ғи®ҫи®Ўз”ЁдәҺж”№е–„е·ҘдҪңиҙҹиҪҪдјҳеҢ–е№іеҸ°зҡ„дә’иҝһгҖӮжҲ‘们жҢҒз»ӯеҠ ејәеҸ°з§Ҝз”өеңЁжҠҖжңҜйўҶе…Ҳең°дҪҚгҖҒеҚ“и¶ҠеҲ¶йҖ е’Ңе®ўжҲ·дҝЎд»»ж–№йқўдёүдҪҚдёҖдҪ“зҡ„дјҳеҠҝпјҢиҝҷи®©жҲ‘们иғҪеӨҹе……еҲҶж»Ўи¶іжҜҸдҪҚе®ўжҲ·зҡ„иҰҒжұӮгҖӮгҖҚ

дә§е“Ғдҫӣиҙ§жғ…еҶө

AriesеӨҚдҪҚж—¶еҷЁдә§е“Ғз»„еҗҲж”ҜжҢҒPCIe 4.0е’ҢPCIe 5.0жһ¶жһ„пјҢжҸҗдҫӣx16гҖҒx8е’Ңx4и§„ж је°әеҜёгҖӮиө„жәҗ

еҪұзүҮ:PCIeеӨҚдҪҚж—¶еҷЁжҰӮи§ҲйғЁиҗҪж ј:PCI ExpressеӨҚдҪҚж—¶еҷЁVSйҮҚй©ұеҠЁпјҡжғҠдәәзҡ„е·®ејӮ

жј”зӨә:PCI ExpressеӨҚдҪҚж—¶еҷЁдёҺNVMe SSDзҡ„еә”з”Ё

зҪ‘з»ңз ”и®Ёдјҡ:жӢҜж•‘иҖ…еӨҚдҪҚж—¶еҷЁ (ж–°й—»жқҘжәҗпјҡAstera Labs е®ҳзҪ‘)